#### 1. Electro-Static Discharge (ESD) Test Results

#### **1.1 Test Description**

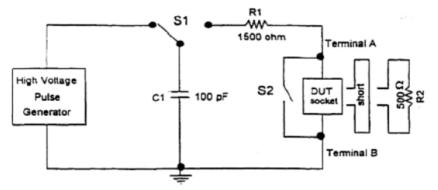

The HBM ESD testing was performed on a THERMOFISHER Mk.2 using the Human Body Module per ANSI/ESDA/JEDEC JS-001-2012. This test is performed for classification only. Class 1A >±250V, Class 1B >±500V, Class 1C >±1000V, Class 2 >±2000V, Class 3A >±4000V and Class 3B >±8000V. A copy of the circuit is shown below:

#### **1.2 Test Circuit & Condition**

Figure 1 — Typical equivalent HBM ESD circuit

NOTE 1 The performance of any simulator is influenced by its parasitic capacitance and inductance.

NOTE 2 Precautions must be taken in tester design to avoid recharge transients and multiple pulses.

NOTE 3 R2, used for initial equipment qualification and requalification as specified in 3.1, shall be a low inductance, 4000 V, 500  $\Omega$  resistor with +/-1% tolerance.

NOTE 4 Stacking of DUT socket adaptors (piggybacking) is allowed only if the waveforms can be verified to meet the specifications in Table 1.

NOTE 5 Reversal of terminals A and B to achieve dual polarity is not permitted.

NOTE 6  $\,$  S2 shall be closed at least 10 milliseconds after the pulse delivery period to ensure the DUT socket is not left in a charged state.

NOTE 7 R1,1500 Ω +/- 1%.

NOTE 8 C1, 100 pF +/- 10% (effective capacitance).

# 1.3 ESD Data

|                   |          |     |          | Voltage |                |

|-------------------|----------|-----|----------|---------|----------------|

| Device            | Model    | S/S | Pins     | Passed  | Voltage Failed |

| LTC3636EUFD#TRPBF | HBM      | 3   | All Pins | >±1500V | <±2000V        |

|                   | Class 1C |     |          |         |                |

|                   |          |     |          |         |                |

|                   |          |     |          |         |                |

1.4 Test Description

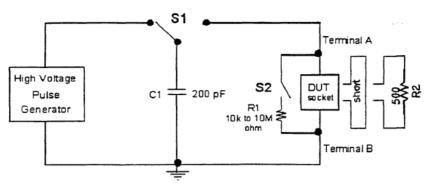

The Machine Model (MM) ESD testing was performed on a THERMOFISHER Mk.2 using the Machine Model Module per JESD22-A115A. **Class A <±200V, Class B >±200V and Class C >±400V**. This test is performed for information only. A copy of the circuit is shown below:

1.5 Test Circuit & Condition

Figure 1 — Typical equivalent MM ESD circuit

#### NOTES

1 The performance of any simulator is influenced by its parasitic capacitance and inductance.

2 Precautions must be taken in tester design to avoid recharge transients and multiple pulses.

3 R2, used for initial equipment qualification and requalification as specified in 3.1, shall be a low inductance, 1000 volt, 500 ohm resistor with +/-1% tolerance.

4 Stacking of DUT socket adaptors (piggybacking) is allowed only if the waveforms can be verified to meet the specifications in table 1.

5 Reversal of terminal A and B to achieve dual polarity is not permitted.

$6\,$  S2 should be closed 10 to 100 milliseconds after the pulse delivery period to ensure the DUT socket is not left in a charged state.

7 C1, 200 pF +/- 10%.

# 1.6 ESD Data

| Device            | Model       | S/S | Pins           | Voltage<br>Passed | Voltage Failed |

|-------------------|-------------|-----|----------------|-------------------|----------------|

| LTC3636EUFD#TRPBF | MM<br>Class | 3   | Not Applicable |                   |                |

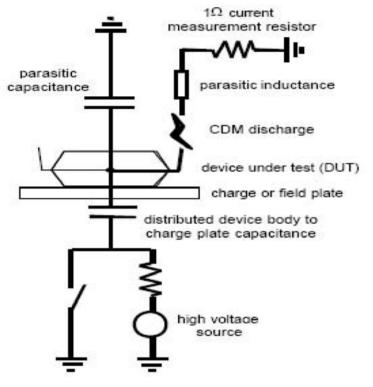

# **1.7 Test Description**

The Charged Device Model (CDM) ESD testing was performed on a THERMOFISHER RCDM system per ESDA ESD ANSI/ESD S5.3.1-2009. This test is performed for information only. A copy of the circuit is shown below:

# **1.8 Test Circuit & Condition**

## 1.9 ESD Data

| Device            | Model | S/S | Pins     | Voltage<br>Passed | Voltage Failed |

|-------------------|-------|-----|----------|-------------------|----------------|

| LTC3636EUFD#TRPBF | CDM   | 3   | All Pins | >±2000V           |                |

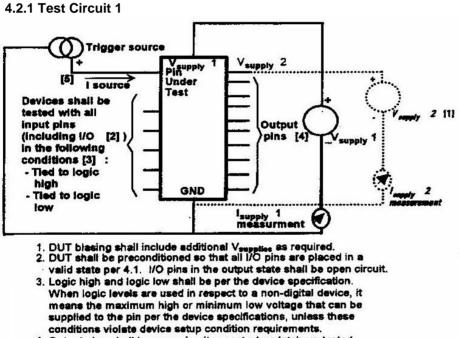

#### 4. Latch-Up Test Results

# 4.1 Test Description

Latchup Testing was performed at +25°C and +90°C using the LTX Integrated Circuit Test system. The Power Supply pins are biased to the appropriate Datasheet specifications and the individual non-Power Supply pins are tested incrementally while the current is monitored until failure occurs.

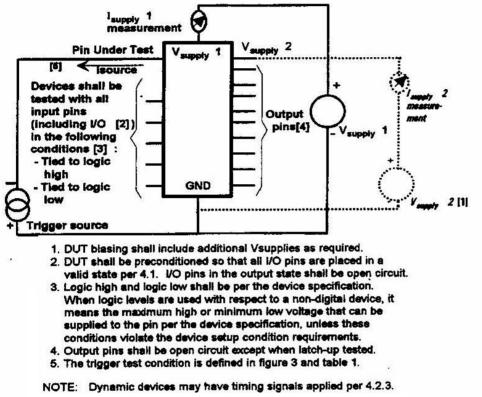

4.2 Test Circuit & Condtion

- 4. Output pins shall be open circuit except when latch-up tested.

- 5. The trigger test condition is defined in figure 2 and table 1.

NOTE: Dynamic devices may have timing signals applied per 4.2.3.

# 4.2.2 Test Circuit 2

| Device            | Mode | Current | Temp   | S/S | Results |  |  |

|-------------------|------|---------|--------|-----|---------|--|--|

| LTC3636EUFD#TRPBF | CKT1 | >±200mA | +25°C  | 5   | PASS    |  |  |

|                   | CKT2 | >±200mA | +25⁰C  | 5   | PASS    |  |  |

|                   | CKT1 | >±200mA | +130°C | 5   | PASS    |  |  |

|                   | CKT2 | >±200mA | +130°C | 5   | PASS    |  |  |

|                   |      |         |        |     |         |  |  |

4.3 Latch-Up Data